上次尝试叠焊闪存的时候出师不利烧了两片 K9GBG08U0A 以及一块 UP19 的板子,给我留下了不小的心理阴影。但是这件事情造成的最严重的后果倒不是白白浪费 40 多软妹币,而是脑子里总有个想法挥之不去,那就是一定要再搞个叠焊出来试试,叠不成功死不休啊。于是就有了下文。

这次的材料不再是便宜的两片 4GB MLC NAND 再加上白菜价 UP19 主控板,而是总价 ¥70 的两片 8GB 的 MT29F64G08CBAAA ,外加十块多钱的 IT1167B 主控板。这样的待遇你丫不好意思再失败了吧?闪存依然是 1CE 的,这样跳线非常方便,只用短路相邻的 CE 跟 RB 脚就可以了。而对于 IT1167 这样共用 RB 脚的主控,RB 脚就不用跳了,直接焊在一起就行了。

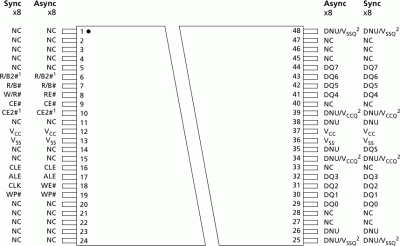

以上是闪存叠焊的理论基础—— NAND 闪存引脚图。可以看见,2CE 的芯片和 1CE 芯片唯一的区别就是有两个状态脚( RB )和片选脚( CE )(这不是废话么 =。=)。但是,接下来的一点非常重要,那就是 CE1 跟 CE2 是相邻的,RB1 跟 RB2 也是相邻的。这就意味着,我们完全可以把两块单 CE 的闪存叠起来,除了 RB 跟 CE 跳接以外其他全部并联,而 RB 跟 CE 也只需要往相邻的位置挪挪,然就就得到了一个 2CE 的闪存,容量和写入速度可以加倍。

对于共用 RB 的主控,由于 RB 全部并联,所以 RB 也不用跳接了,直接像其它针脚一样并联就行,也就是说总共就需要跳接一个片选脚。

理论部分结束,下面开始实战。

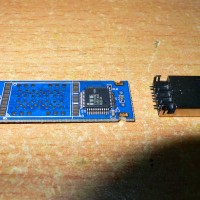

先看看用到的主控板,数码之家出的 IT1167B 双通道防烧写保护的板子。使用这个板子要注意几点:

- 仔细观察闪存的焊盘,所有 RB 都是并联在一起的,因此 RB 脚不用跳线,你若非要跳,请往富士康;

- 这个板子的焊盘巨容易掉,很多人都在这栽了。所以焊的时候时刻注意观察,不要长时间高温烘烤,不要拿烙铁头掰闪存的引脚;

- 闪存的焊盘宽度还算厚道,但是有一侧离主控太近了。如果焊的时候主控搭锡了,不必惊慌,拿锡泵处理掉就行了,跟闪存一样的。注意把锡渣清理干净,短路烧主控就不好了;

- 量产的时候开写保护属于 2B 行为。

嗯,要注意的应该就只有上面这些了。

下面就是准备闪存了。闪存推荐用 1CE 的,这样跳线很方便,否则还需要飞两根漆包线,这样跪掉的可能性又大了不少。上层片一定要用全新未上过锡的闪存制作,否则引脚不易彻底掰直,容易因为接触不到下层片的引脚而虚焊。

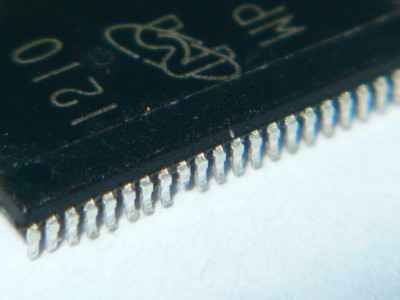

下面开始上层片的制备(下层片很好焊,愿意看这玩意的应该都焊到吐了,因此不再赘述)。首先拿刀背把闪存两侧的引脚都压直,注意不能影响引脚之间的间距,越直越好。(爷都开始拍教程照片了,丫好意思不成功么?!)

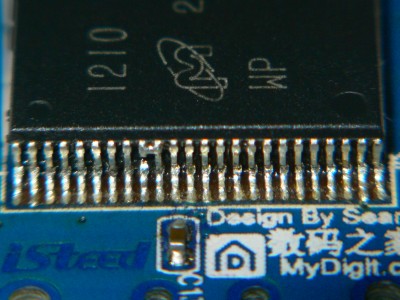

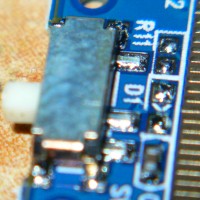

然后把 1-8 脚压下去,留下 9 号引脚,他就是 CE 了。我们将它微微抬起,然后拿指甲剪给它剪断一点,以免碰到下层片的 CE (那样就悲剧了,十有八九要烧)。然后剩下的针脚也全部压下去,成直角朝下。

最后准备好的上层片就是这样了。注意 CE 脚缺了一块。给这些针脚全部上锡。

然后叠在下层片上,刷一遍,基本就焊好了。然后给烙铁头加一点锡,让 9 号针脚和 10 号针脚搭锡,这样 CE 的跳线就完成了。

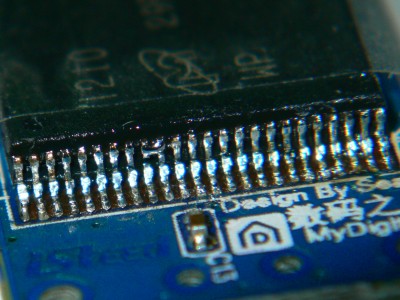

不过有一些针脚看起来似乎焊虚了,先上机看看情况如何。

然后果断就悲剧了,清空到 50% 主控失去响应,目测上层片的 RB 虚焊了。

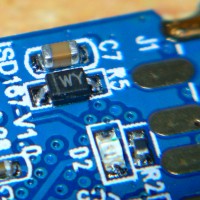

于是痛下决心补焊,弄适量焊锡在引脚上,加些松香,拿烙铁在上下两片闪存针脚连接的位置来回拖焊,确认所有针脚都焊好以后继续加把松香然后拿烙铁头把多余的锡都吸引下来。最后别忘了重新搭锡跳线。

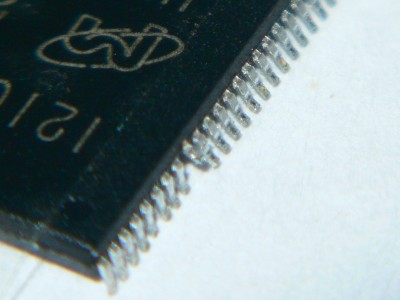

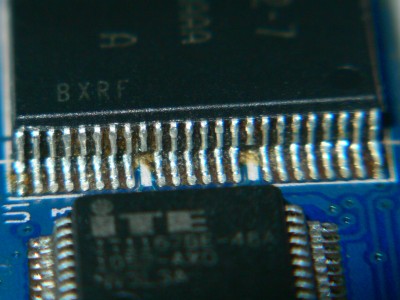

松香太恶心了,全部刮掉。这样引脚的状况就看得比较清楚了。

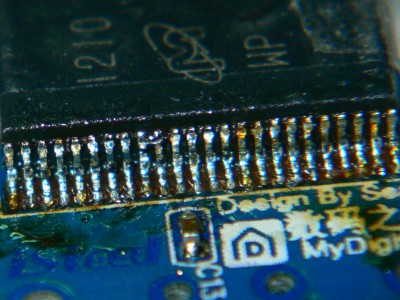

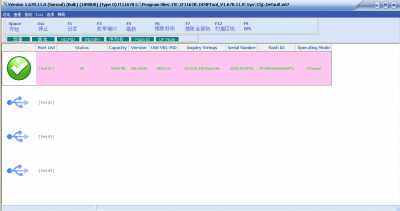

再次上机量产,果然就成功了,看来数据脚那边没啥问题。量产过程中做了 5% 的文件拷贝测试。

为了保险起见,数据脚那一侧也重新加锡焊了一遍,这样看上去就踏实多了。

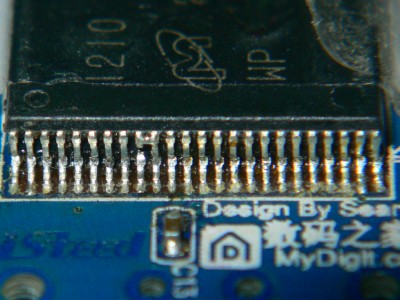

试了医用酒精、美工刀、牙刷,里面的松香就是掏不出来。算了,就这样吧,手贱把闪存掏下来就不好了 =_=b 。

另一侧也洗一下,这样有看相多了。

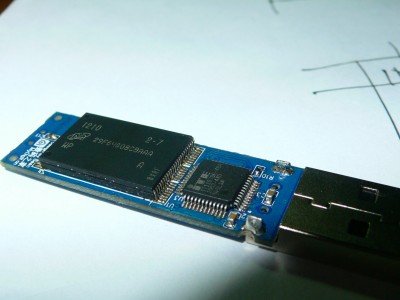

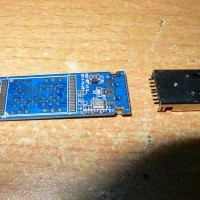

最后来个整体效果图。

后续会继续买两片闪存完成另外一个通道的叠焊,这样 IT1167B 的速度才能完全发挥出来。

(不过 32GB 的 U 盘真的大丈夫?)